Parallel To Serial Converter Vhdl Program

Xilinx Glossary. BOne- decibel compression point. PAPower Amplifier. PACEPinout Area Constraints Editor. A GUI tool that defines legal pin assignments and.

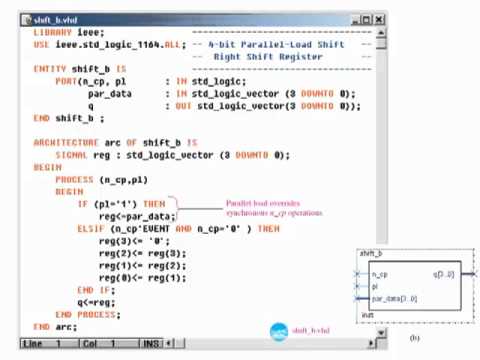

Contents. Shift Register VHDL Code for shift register can be categorised in serial in serial out shift register, serial in parallel out shift register, parallel in parallel out shift register and parallel in serial out shift register. Parallel In – Parallel Out Shift Registers For parallel in – parallel out shift registers, all data bits appear on the parallel outputs immediately following the simultaneous entry of the data bits. The following circuit is a four-bit parallel in – parallel out shift register constructed by D flip-flops. The D’s are the parallel inputs and the Q’s are the parallel outputs. Once the register is clocked, all the data at the D inputs appear at the corresponding Q outputs simultaneously.

Parallel To Serial Converter

VHDL code for Parallel In Parallel Out Shift Register library ieee; use ieee.stdlogic1164.all; entity pipo is port( clk: in stdlogic; D: in stdlogicvector(3 downto 0); Q: out stdlogicvector(3 downto 0) ); end pipo; architecture arch of pipo is begin process (clk) begin if (CLK'event and CLK='1') then Q.